Published in IET Circuits, Devices & Systems Received on 23rd November 2010 Revised on 10th May 2011 doi: 10.1049/iet-cds.2010.0401

ISSN 1751-858X

# Small-signal analysis of fully-differential closed-loop op-amp circuits with arbitrary external impedance elements

J.J. Cooley A.-T. Avestruz S.B. Leeb

Massachusetts Institute of Technology, MIT RM 10-069, 77 Massachusetts Avenue, Cambridge, MA 02139, USA E-mail: jjcooley@mit.edu; cooleymobile@gmail.com

**Abstract:** An analytical modelling approach for fully differential amplifiers is presented and validated through examples. Separation of the analysis into two steps coupled with linear superposition techniques leads to concise mathematical expressions. An added benefit of the two-step approach is that the usual symmetry assumptions are not needed. As a consequence, the results hold for arbitrary element values. The mathematical results are validated by comparison to SPICE simulations and experimental data.

### 1 Introduction

Fully differential (FD) amplifiers afford notable benefits in dynamic range and rejection of unwanted signals. The dynamic range benefit is significant when contending with low supply voltages in fully integrated and system-on-chip design [1-7], general purpose and audio frequency instrumentation [4, 8-10] and in discrete op-amp applications particularly for accommodating dynamic mode (DM) input analogue to digital converters [9-13]. Integrated switched capacitor amplifiers have exploited this benefit as well [14-17]. Power supply disturbances and common-mode (CM) pickup constitute typical unwanted signals that are better rejected by FD electronics when compared to their single-ended (SE) counterparts [8, 14, 18-21]. Both voltage-mode and current-mode (transimpedance) FD amplifiers are useful as front-end amplifiers for suppressing unwanted carrier content in balanced or 'bridge-like' systems [22-25]. Additionally, DM signal processing rejects the effects of even-order nonlinearities [11, 20]. Both balanced and intentionally asymmetric FD amplifiers play important roles [10, 13].

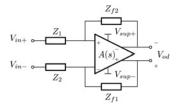

These benefits come at the expense of added complexity in analysis. Powerful simplifications are possible upon assuming perfect or almost perfect symmetry, for example, equality between homologous elements,  $Z_{f1}$  and  $Z_{f2}$ , in Fig. 1. References [20, 26–28] exploit those simplifications to develop half-circuit decomposition methods. In [10] the author analyses FD amplifiers directly, but relies on perfect symmetry assumptions late in the analysis to arrive at expressions in terms of DM or CM input signals.

This work takes an alternative approach to the analysis of FD amplifiers. The analysis is separated into two steps corresponding to the inner transimpedance amplifier and the outer voltage-mode amplifier. Linear superposition of CM

and DM signals assures that the results are written directly in terms of those quantities. Separation of the analysis and the use of linear superposition lead to concise or 'low-entropy' mathematical expressions [29]. An added benefit of the approach is that the usual symmetry assumptions are not needed and so the results hold for arbitrary element values.

The development of the FD transimpedance amplifier circuit model in Section 2 is perhaps the core contribution of this work. The versatility of that circuit model is demonstrated in three key contexts. First, the transimpedance amplifier model is used to derive the performance of a voltage amplifier with arbitrary impedance elements,  $Z_1$  and  $Z_2$  in Fig. 1. The results hold for arbitrary impedance values and agree well with the simulated behaviour of a commercial FD op-amp. Second, the extension of that analysis to include finite op-amp input impedance using the same transimpedance amplifier circuit model is described. Finally, the transimpedance amplifier model is used to predict the behaviour of a capacitive bridge sensor system. In the capacitive bridge sensor system, the external impedance elements  $Z_1$  and  $Z_2$  are further generalised to an arbitrary impedance network. Finite op-amp input impedance is captured by including shunt impedances at the transimpedance amplifier circuit model inputs. In the capacitive bridge sensor system, the front-end amplifier is loaded by the subsequent synchronous demodulation circuitry. Model validation comparing experimental data to data simulated using the transimpedance amplifier circuit model shows excellent agreement.

# 1.1 Current paths in FD amplifiers

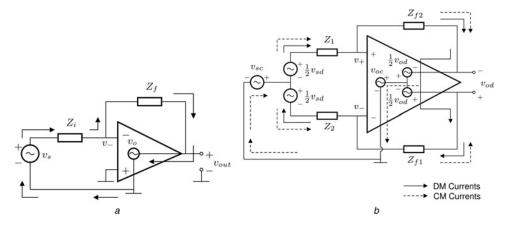

The ensuing analysis will be better appreciated having an understanding of the CM and DM current paths through a FD amplifier. The current paths in the FD amplifier

Fig. 1 FD closed-loop op-amp circuit

(Fig. 2b) are in some sense a generalisation of those in the SE amplifier (Fig. 2a); current return paths are supported by the output structure of the op-amp itself, but in the FD amplifier purely DM and purely CM currents take two distinct paths. The circuit models developed through the analysis in Sections 2 and 3 will mirror the current paths shown in Fig. 2b. Note that the incremental grounds in Fig. 2 are physically supported by the op-amp power supply connections. Incremental grounds are those potential surfaces exhibiting purely DC voltages with respect to the actual system ground.

### 1.2 Definitions

Definitions of CM and DM signal decompositions vary among the literature. We define them in this work as follows

$$v_{\rm dm} = v_+ - v_- \tag{1}$$

$$v_{\rm cm} = \frac{v_+ + v_-}{2} \tag{2}$$

$$i_{\rm dm} = \frac{i_+ - i_-}{2}$$

(3)

$$i_{\rm cm} = i_+ + i_-$$

(4)

# 1.3 Scope

The analysis in Sections 2 and 3 focuses on the DM output voltage while the CM output voltage is assumed to be held fixed by the CM feedback circuit included in all commercial FD op-amps. The scope of this paper is intended to address op-amp circuits that process signals having frequency content well below the op-amp cross-over frequency, for example, 1 kHz in the simulations of the LTC6404. These cases are ubiquitous as they are coincident

with good design practices guaranteeing that the op-amp will exhibit large DM-DM gain,  $a_{\rm d}$ , and relatively small CM-DM gain,  $a_{\rm c}$ . Loading effects on the closed-loop op-amp circuit are negligible under these conditions because the feedback control significantly reduces the effect of finite-op-amp (open-loop) output impedance. The assumptions described above will be validated in both simulation and in a practical setting in Section 4.

## 1.4 Dynamics

The results in this paper are derived in terms of op-amp gain parameters,  $a_{\rm d}$  and  $a_{\rm c}$ , and generalised external impedance elements. The behaviour of an arbitrary system having dynamic effects may be described by inserting the frequency dependencies of those parameters into the mathematical results or circuit models.

### 1.5 Model validation

Comparison of the mathematical results with the simulated and experimental data validates the assumptions taken in the analysis, the practical relevance of this work and the correctness of the mathematical manipulations. Simulated model validation was carried out by comparing numerical results from the mathematical results to SPICE simulations of ideal circuit models and of a commercial FD op-amp, the LTC6404. The commercial LTC6404 FD op-amp part was chosen for the model validations because of the availability of a SPICE model for that part in the library provided with the simulation software used here, LTSPICE. The model validations plot the quantities of interest against percentage mismatch between homologous elements, e.g.  $\Delta Z$  is the mismatch between  $Z_1$  and  $Z_2$  in Fig. 1. 0% mismatch corresponds to perfect symmetry. 200% mismatch means that one element is zero-valued while the other is twice the average value.

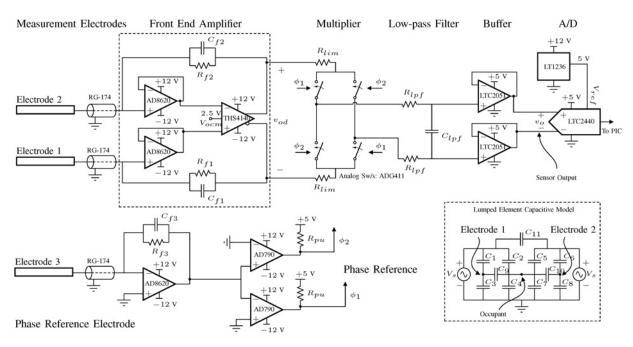

Experimental model validation was carried out by comparing simulated data to experimental data in a practical setting involving macroscopic capacitive occupancy sensing and a synchronous detection signal processing system. The commercial FD op-amp employed in that experimental setup was the Texas Instruments part, THS4140. While a SPICE model was not readily available for the THS4140 part, only the linearised circuit model developed in this paper was needed in the experimental model validation for

Fig. 2 Small-signal current paths in closed-loop op-amp amplifiers

a SE

b FD

Section 4. The model parameters inserted into the linearised circuit model can be taken from the data sheet for that part, which was readily available.

# 2 Analysis step one: transimpedance amplifier

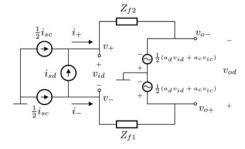

In this section we analyse a FD transimpedance amplifier using the small-signal model shown in Fig. 3. In the small-signal model, the input and output voltages are

$$v_{\rm id} = v_+ - v_- \tag{5}$$

$$v_{\rm ic} = \frac{1}{2}(v_+ + v_-) \tag{6}$$

$$v_{\rm od} = v_{o+} - v_{o-} \tag{7}$$

The DM and CM input currents are respectively

$$i_{\rm id} = i_{\rm sd} = \frac{1}{2}(i_+ - i_-)$$

(8)

$$i_{\rm ic} = i_{\rm sc} = i_+ + i_-$$

(9)

and the amplifier has the effects

$$v_{\rm od} = a_{\rm d}v_{\rm id} + a_{\rm c}v_{\rm ic} \tag{10}$$

$$v_{o+} = -v_{o-} \tag{11}$$

where  $a_d$ , the DM-DM op-amp gain, is large by design and  $a_c$ , the CM-DM op-amp gain, is relatively small, also by design. The small-signal CM output voltage is an incremental ground.

## 2.1 Transimpedance amplifier output behaviour

A CM-DM superposition approach for determining the transimpedance amplifier's DM output voltage is summarised by the equation

$$v_{\text{od}} = i_{\text{id}} \left( \frac{v_{\text{od}}}{i_{\text{id}}} \right)_{i_{\text{ic}} = 0} + i_{\text{ic}} \left( \frac{v_{\text{od}}}{i_{\text{ic}}} \right)_{i_{\text{id}} = 0}$$

(12)

in which the terms in parentheses are the transimpedance and cross-transimpedance. To find  $(v_{\rm od}/i_{\rm id})_{i_{\rm ic}=0}$ , the CM input current sources are deactivated. Note that in this case

$$i_{\rm id} = i_{\rm sd} = i_{\perp} = -i_{\perp}$$

(13)

Fig. 3 FD transimpedance amplifier small-signal model

From Fig. 3, the resulting input terminal voltages are

$$v_{+} = v_{o-} + i_{id} Z_{f2} \tag{14}$$

$$v_{-} = v_{o+} - i_{id} Z_{f1} \tag{15}$$

so that, from (5) and (6), the CM and DM input voltages become

$$v_{\rm ic} = \frac{1}{2}(v_+ + v_-) = \frac{i_{\rm id}}{2}(Z_{f2} - Z_{f1})$$

(16)

$$v_{\rm id} = v_+ - v_- = -v_{\rm od} + i_{\rm id}Z_{f2} + i_{\rm id}Z_{f1}$$

(17)

Substituting the CM and DM input voltages into the output voltage from (10) yields

$$v_{\text{od}} = a_{\text{d}}(i_{\text{id}}(Z_{f1} + Z_{f2}) - v_{\text{od}}) + a_{\text{c}} \frac{i_{\text{id}}}{2}(Z_{f2} - Z_{f1})$$

(18)

so that

$$\left(\frac{v_{\text{od}}}{i_{\text{id}}}\right)_{i_{\text{in}}=0} = 2\frac{a_{\text{d}}}{1+a_{\text{d}}}\overline{Z_f} - \frac{a_{\text{c}}}{2(1+a_{\text{d}})}\Delta Z_f \tag{19}$$

where we have made the following definitions

$$\overline{Z_f} \equiv \frac{(Z_{f1} + Z_{f2})}{2} \tag{20}$$

$$\Delta Z_f \equiv Z_{f1} - Z_{f2} \tag{21}$$

To calculate  $(v_{\rm od}/i_{\rm ic})_{i_{\rm id}=0}$ , the DM input current source is deactivated. A similar analysis yields

$$\left(\frac{v_{\text{od}}}{i_{\text{ic}}}\right)_{i_{\text{id}}=0} = \frac{1}{2} \frac{\left(-a_{\text{d}} \Delta Z_f + a_{\text{c}} \overline{Z_f}\right)}{\left(1 + a_{\text{d}}\right)}$$

(22)

Superposing the two responses in (19) and (22) yields the complete expression for the DM output voltage in response to generalised input currents

$$v_{\rm od} = i_{\rm id} \left( \frac{2a_{\rm d}\overline{Z_f} - (1/2)a_{\rm c}\Delta Z_f}{(1+a_{\rm d})} \right) + i_{\rm ic} \left( \frac{a_{\rm c}\overline{Z_f} - a_{\rm d}\Delta Z_f}{2(1+a_{\rm d})} \right)$$

(23)

# 2.2 Transimpedance amplifier input behaviour

Having derived the DM output voltage, a similar analysis leads to the DM and CM input voltages. These results will be grouped according to the superposition expressions below

$$v_{\rm id} = i_{\rm id} \left(\frac{v_{\rm id}}{i_{\rm id}}\right)_{i_{\rm ic}=0} + i_{\rm ic} \left(\frac{v_{\rm id}}{i_{\rm ic}}\right)_{i_{\rm id}=0}$$

(24)

$$v_{\rm ic} = i_{\rm id} \left(\frac{v_{\rm ic}}{i_{\rm id}}\right)_{i_{\rm ic}=0} + i_{\rm ic} \left(\frac{v_{\rm ic}}{i_{\rm ic}}\right)_{i_{\rm id}=0}$$

(25)

Analysing the small-signal model in Fig. 3 leads to

$$v_{\rm ic} = -i_{\rm id} \frac{\Delta Z_f}{2} + i_{\rm ic} \frac{\overline{Z_f}}{2}$$

(26)

and

$$v_{\rm id} = i_{\rm id} \left( \frac{2\overline{Z_f} + \frac{1}{2}a_{\rm c}\Delta Z_f}{(1+a_{\rm d})} \right) - i_{\rm ic} \left( \frac{\Delta Z_f + a_{\rm c}\overline{Z_f}}{2(1+a_{\rm d})} \right)$$

(27)

Comparing these results to (24) and (25) reveals the distinct terms resulting from the superposition of the CM and DM input sources. An interesting pattern arises in the results above. Terms with one of  $a_c$  or  $\Delta Z_f$  influence crosscoupling from CM to DM signals. On the other hand, terms with a product of  $a_c$  and  $\Delta Z_f$  appear as non-ideal terms in the relation between two DM signals. This pattern is intuitive and ubiquitous in this paper.

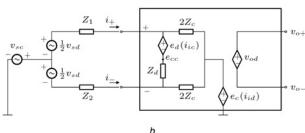

# 2.3 Circuit models of the transimpedance amplifier

For the second step of the analysis, it will be useful to form circuit models of the transimpedance amplifier. Figs. 4b and c show 'T' and 'II' topologies that are helpful for representing the CM and DM input voltages in (26) and (27). Both models include a dependent voltage source at the output, which captures the function of the transimpedance and the cross-transimpedance from (23). The two models differ in their input structures. The T-network and the II-network are each intended to approximate the behaviour of the CM and DM input voltages in (26) and (27).

To simplify the following discussion, it is convenient to rename the terms in (26) and (27) as follows

$$Z_{\rm c} \equiv \left(\frac{v_{\rm ic}}{i_{\rm ic}}\right)_{i_{\rm c}=0} = \left(\frac{\overline{Z_f}}{2}\right) \tag{28}$$

$$Z_{\rm d} \equiv \left(\frac{v_{\rm id}}{i_{\rm id}}\right)_{i_{\rm is}=0} = \left(\frac{2\overline{Z_f} + (1/2)\Delta Z_f a_{\rm c}}{(1+a_{\rm d})}\right)$$

(29)

$$e_{\rm c}(i_{\rm id}) \equiv i_{\rm id} \left(\frac{v_{\rm ic}}{i_{\rm id}}\right)_{i_{\rm io}=0} = -i_{\rm id} \left(\frac{\Delta Z_f}{2}\right)$$

(30)

$$e_{\rm d}(i_{\rm ic}) \equiv i_{\rm ic} \left(\frac{v_{\rm id}}{i_{\rm ic}}\right)_{i_{\rm id}=0} = -i_{\rm ic} \left(\frac{\Delta Z_f + a_{\rm c} \overline{Z_f}}{2(1+a_{\rm d})}\right) \tag{31}$$

The terms  $Z_c$  and  $Z_d$  are the diagonal-terms from (26) and (27) and they are the CM and DM input impedances of the transimpedance amplifier. The terms  $e_c(i_{id})$  and  $e_d(i_{ic})$  represent dependent voltage sources that capture the effects of the 'cross-terms' in (26) and (27).

Using the definitions in (28)–(31), the following model parameters achieve an exact match between the terminal behaviours of the circuits in Figs. 4b and c and the input voltages represented by (26) and (27)

T-Model: Π-Model:

$$Z_{\alpha} = Z_{\rm d} \qquad \qquad Z_{\gamma} = Z_{\rm d} \frac{Z_{\rm d}}{Z_{\rm d} ||4Z_{\rm c}||} \tag{32}$$

$$Z_{\beta} = Z_{c} \qquad \qquad Z_{\delta} = Z_{c} \tag{33}$$

$$e_{\alpha} = e_{\mathrm{d}}(i_{\mathrm{ic}}) \qquad \qquad e_{\gamma} = e_{\mathrm{d}}(i_{\mathrm{ic}}) \frac{Z_{\mathrm{d}}}{Z_{\mathrm{d}} ||4Z_{\mathrm{c}}|}$$

(34)

$$e_{\beta} = e_{\rm c}(i_{\rm id}) - \frac{i_{\rm ic}Z_{\rm d}}{4} \quad e_{\delta} = e_{\rm c}(i_{\rm id}) \tag{35}$$

The model parameters in (32)–(35) can be simplified under practical approximations to make the circuit models more intuitive. For sufficiently small  $Z_d$ , the additive term,  $(i_{ic}Z_d)$

Fig. 4 FD transimpedance amplifier and two approximate small-signal models

a FD transimpedance amplifier

b Small-signal T-model

c Small-signal  $\Pi$ -model

T-model and the  $\Pi$ -model differ in the structure of their input network. Each contain an internal node labelled  $e_{cc}$

4), will approach zero and the multiplicative term,  $(Z_d | 4Z_c)$ , will approach unity. From (28)–(31),  $Z_d$  is guaranteed to be small if both  $a_d$  and the ratio  $a_d/a_c$  are large. Under these assumptions, the model parameters in (32)–(35) reduce to

T-Model: Π-Model:

$$Z_{\alpha} = Z_{\rm d} \quad Z_{\gamma} = Z_{\rm d} \tag{36}$$

$$Z_{\beta} = Z_{c} \quad Z_{\delta} = Z_{c} \tag{37}$$

$$e_{\alpha} = e_{\mathsf{d}}(i_{\mathsf{ic}}) \quad e_{\gamma} = e_{\mathsf{d}}(i_{\mathsf{ic}}) \tag{38}$$

$$e_{\beta} = e_{c}(i_{id}) \quad e_{\delta} = e_{c}(i_{id}) \tag{39}$$

For simplicity, the rest of this analysis assumes that the gain criteria above have been met and proceeds with the approximate model parameters in (36)–(39).

# 2.4 Transimpedance amplifier model validation

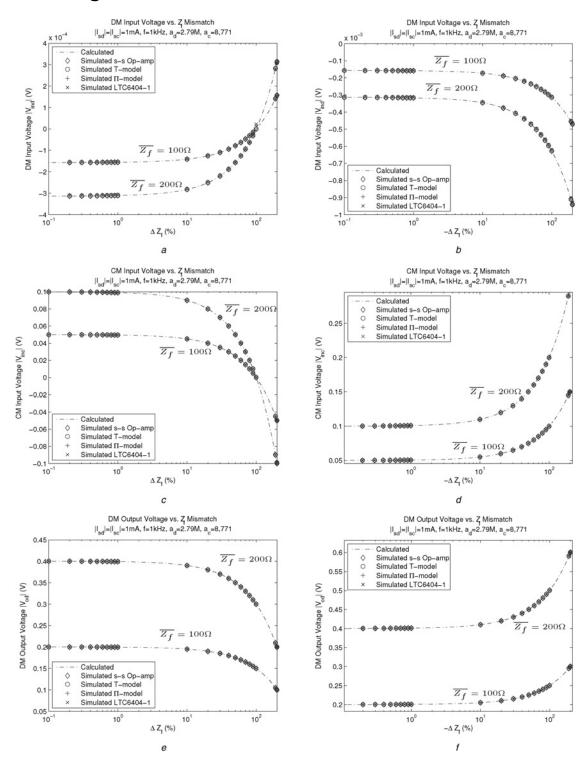

Fig. 5 shows model validation plots for the transimpedance amplifier. In the model validations, the amplifier was driven with a 1 kHz sinusoidal current source with equal CM and DM components each having an amplitude of 1 mA. The calculated results for  $v_{\rm id}$ ,  $v_{\rm ic}$  and  $v_{\rm od}$  were overlayed on the simulated results for the T and  $\Pi$  circuit models, a small-signal ('s-s') op-amp model and a simulated commercial op-amp. The left column in Fig. 5 shows results for positive-valued mismatches,  $\Delta Z_f$ . The right column shows results for negative-valued mismatches. The results in Fig. 5 show good agreement among the calculated and simulated results.

# 2.5 Virtual short-circuit approximation

From (29), the impedance of the DM virtual short-circuit is predominantly  $2\overline{Z_f}/(1+a_{\rm d})$ . The DM gain,  $a_{\rm d}$ , is large by design, so this impedance is small and hence the virtual short-circuit approximation. On the other hand, the CM input impedance in (28) is half the average feedback impedance – approximately equal to  $Z_{f1}\|Z_{f2}$  for small mismatch values. These results become intuitive when following the respective current paths (Fig. 2b) through the amplifier.

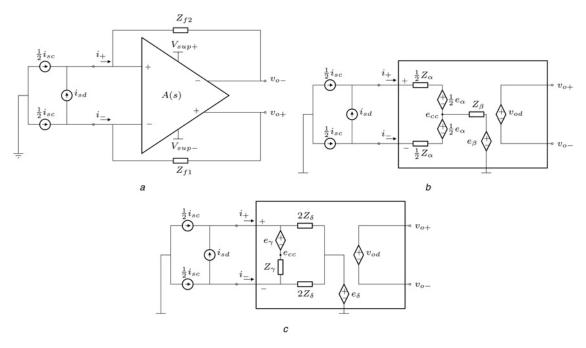

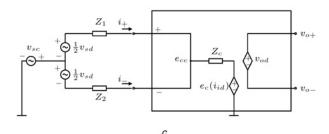

# 3 Analysis step two: voltage amplifier

In Fig. 6, input elements  $Z_1$  and  $Z_2$  are added onto the  $\Pi$ -model of the transimpedance amplifier circuit model to form a voltage amplifier model. The goal of this section is to find the DM output voltage,  $v_{\rm od}$ , that results from the CM and DM input voltages,  $v_{\rm sc}$  and  $v_{\rm sd}$ . The transimpedances derived in Section 2 reveal the relationships between the input currents,  $i_{\rm ic}$  and  $i_{\rm id}$ , and the DM output voltage,  $v_{\rm od}$ , from (23). The voltage amplifier analysis reduces to finding the relationships between the input voltage sources,  $v_{\rm sc}$  and  $v_{\rm sd}$ , and the input currents,  $i_{\rm ic}$  and  $i_{\rm id}$ . This analysis results in four transconductances.

A superposition approach to find the overall DM output voltage yields the following expression

$$v_{\text{od}} = i_{\text{id}} \left( \frac{v_{\text{od}}}{i_{\text{id}}} \right)_{i_{\text{i..}} = 0} + i_{\text{ic}} \left( \frac{v_{\text{od}}}{i_{\text{ic}}} \right)_{i_{\text{i..}} = 0}$$

$$(40)$$

where the terms in parentheses are the two transimpedances from Section 2. The currents,  $i_{id}$  and  $i_{ic}$  in (40), may be

found using linear superposition of the DM and CM input voltage sources as follows

$$v_{\text{od}} = \underbrace{\left(v_{\text{sd}} \left(\frac{i_{\text{id}}}{v_{\text{sd}}}\right)_{v_{\text{sc}}=0} + v_{\text{sc}} \left(\frac{i_{\text{id}}}{v_{\text{sc}}}\right)_{v_{\text{sd}}=0}\right)}_{i_{\text{id}}} \underbrace{\left(\frac{v_{\text{od}}}{i_{\text{id}}}\right)_{i_{\text{ic}}=0}}_{\text{transimpedance}}$$

(41)

$$+\underbrace{\left(v_{\rm sd}\left(\frac{i_{\rm ic}}{v_{\rm sd}}\right)_{v_{\rm sc}=0} + v_{\rm sc}\left(\frac{i_{\rm ic}}{v_{\rm sc}}\right)_{v_{\rm sd}=0}\right)}_{i_{\rm ic}}\underbrace{\left(\frac{v_{\rm od}}{i_{\rm ic}}\right)_{i_{\rm id}=0}}_{\text{cross-transimpedance}}$$

(42)

where the added terms in parentheses are the four transconductances. The two transimpedances and four transconductances can be renamed for brevity as follows

$$Z_{\rm dd} \equiv \left(\frac{v_{\rm od}}{i_{\rm id}}\right)_{i_{\rm ic}=0} \quad Z_{\rm cd} \equiv \left(\frac{v_{\rm od}}{i_{\rm ic}}\right)_{i_{\rm id}=0} \tag{43}$$

$$Y_{\rm dd} \equiv \left(\frac{i_{\rm id}}{v_{\rm sd}}\right)_{v_{\rm co}=0} \quad Y_{\rm cd} \equiv \left(\frac{i_{\rm id}}{v_{\rm sc}}\right)_{v_{\rm cd}=0} \tag{44}$$

$$Y_{\rm dc} \equiv \left(\frac{i_{\rm ic}}{v_{\rm sd}}\right)_{v_{\rm sc}=0} \quad Y_{\rm cc} \equiv \left(\frac{i_{\rm ic}}{v_{\rm sc}}\right)_{v_{\rm sd}=0} \tag{45}$$

so the expression in (42) can be written as

$$v_{\text{od}} = (v_{\text{sd}}Y_{\text{dd}} + v_{\text{sc}}Y_{\text{cd}})Z_{\text{dd}} + (v_{\text{sd}}Y_{\text{dc}} + v_{\text{sc}}Y_{\text{cc}})Z_{\text{cd}}$$

(46)

and regrouped with the source terms

$$v_{\text{od}} = v_{\text{sd}}(Y_{\text{dd}}Z_{\text{dd}} + Y_{\text{dc}}Z_{\text{cd}}) + v_{\text{sc}}(Y_{\text{cd}}Z_{\text{dd}} + Y_{\text{cc}}Z_{\text{cd}})$$

(47)

The analysis may be simplified using the virtual short-circuit approximation quantified in Section 2.5. Analysis of the resulting circuit in Fig. 6c may be divided into four distinct pieces for the four unknown transconductances needed in the expression for  $v_{\rm od}$  (47). Shorting the DM input source results in the set of constraints on the input currents

$$i_{+} = \frac{(v_{\rm sc} - e_{\rm cc})}{Z_{1}} \tag{48}$$

$$i_{-} = \frac{(v_{\rm sc} - e_{\rm cc})}{Z_{2}} \tag{49}$$

while shorting the CM input source results in the set of constraints on the input currents

$$i_{+} = \frac{((1/2)v_{\rm sd} - e_{\rm cc})}{Z_{1}} \tag{50}$$

$$i_{-} = \frac{(-(1/2)v_{\rm sd} - e_{\rm cc})}{Z_2} \tag{51}$$

In either case, the node voltage  $e_{cc}$  in Fig. 6c is constrained to be

$$e_{cc} = e_c + (i_+ + i_-)Z_c (52)$$

Solving for  $i_{\rm id}=(i_+-i_-)/2$  and  $i_{\rm ic}=(i_+-i_-)$  leads to four permutations of constraints corresponding to the four transconductances. For instance, to find  $Y_{\rm dd}$ , the CM input voltage is deactivated according to the definition in (44), and

Fig. 5 Validating the transimpedance amplifier model

$\begin{array}{ll} a \ v_{\mathrm{id}} \ \mathrm{for} \ \Delta Z_f > 0 \\ b \ v_{\mathrm{id}} \ \mathrm{for} \ \Delta Z_f < 0 \\ c \ v_{\mathrm{ic}} \ \mathrm{for} \ \Delta Z_f > 0 \\ d \ v_{\mathrm{ic}} \ \mathrm{for} \ \Delta Z_f < 0 \\ e \ v_{\mathrm{od}} \ \mathrm{for} \ \Delta Z_f > 0 \\ f \ v_{\mathrm{od}} \ \mathrm{for} \ \Delta Z_f < 0 \end{array}$

the DM input current is found from

$$i_{\rm id} = \frac{i_+ - i_-}{2} \tag{53}$$

with the three constraints from KVL above, (50), (51) and

(52). Solving for  $i_{id}/v_{sd}$  and simplifying leads to [30]

$$Y_{\rm dd} = \frac{2\overline{Z_f} + Z_1 + Z_2}{4(Z_1||Z_2 + (1/2)\overline{Z_f})(Z_1 + Z_2) + \Delta Z \Delta Z_f}$$

(54)

**Fig. 6** Adding the input elements onto the transimpedance amplifier model yields a voltage-mode amplifier model

- a FD voltage-mode amplifier

- b Voltage-mode amplifier model built from the  $\Pi$ -model of the transimpedance amplifier

- c Voltage-mode amplifier model using the 'virtual short-circuit approximation'

- d The model used for deriving the correction in Section 3.1

The denominator in  $Y_{\rm dd}$  above appears in all four transconductances. The quantities in that denominator can be identified with respect to physical current paths in the voltage amplifier as follows

$$Z_{\rm dm} = Z_1 + Z_2 \tag{55}$$

$$Z_{\rm cm} = Z_1 || Z_2 + \frac{\overline{Z_f}}{2}$$

(56)

For the simplified model of Fig. 6c,  $Z_{\rm dm}$  is the impedance seen by a purely DM input voltage source driving a purely DM input current and  $Z_{\rm cm}$  is the impedance seen by a purely CM

input voltage source driving a purely CM input current. That is

$$Z_{\rm dm} = \left(\frac{v_{\rm sd}}{i_{\rm id}}\right)_{\substack{v_{\rm sc}=0\\i_{\rm i.e}=0}} \tag{57}$$

$$Z_{\rm cm} = \left(\frac{v_{\rm sc}}{i_{\rm ic}}\right)_{\substack{v_{\rm sd} = 0\\i_{\rm id} = 0}}$$

(58)

Applying the constraints in the four permutations, simplifying and identifying the impedance terms  $Z_{\rm dm}$  and  $Z_{\rm cm}$  leads to

$$Y_{\rm dd} = 2 \frac{\overline{Z_f} + \overline{Z}}{4Z_{\rm cm}Z_{\rm dm} + \Delta Z \Delta Z_f}$$

(59)

$$Y_{\rm cd} = 2 \frac{-\Delta Z}{4Z_{\rm cm}Z_{\rm dm} + \Delta Z \Delta Z_f} \tag{60}$$

$$Y_{\rm dc} = 2\frac{\Delta Z_f - \Delta Z}{4Z_{\rm cm}Z_{\rm dm} + \Delta Z \Delta Z_f} \tag{61}$$

$$Y_{\rm cc} = 8 \frac{\overline{Z}}{4Z_{\rm cm}Z_{\rm dm} + \Delta Z \Delta Z_f}$$

(62)

The common denominator in these transconductances aids further analysis when we form linear combinations of these terms (see Section 3.3).

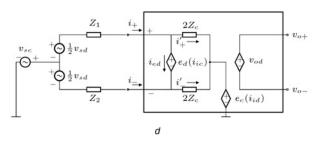

### 3.1 Model correction

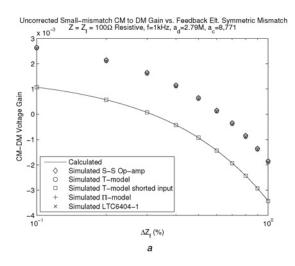

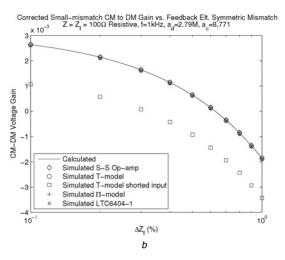

The virtual short-circuit approximation led to some inaccuracy in the results for CM-DM gain,  $A_{\rm vc}$ , in the small-mismatch region (Fig. 7a). The modularity of the results allows for rapid correction of this inaccuracy. Adding the effect of  $e_{\rm d}(i_{\rm ic})$  is most critical for correcting  $A_{\rm vc}$  because it accounts for a DM input voltage in response to a CM input current. Among the two transconductaces that affect CM-DM gain,  $Y_{\rm cd}$  quantifies the DM input current, which is most directly affected by the addition of  $e_{\rm d}(i_{\rm ic})$  to the model. This correction re-derives  $Y_{\rm cd}$  from the circuit in Fig. 6d, while  $Y_{\rm cc}$  is assumed sufficiently accurate.

The circuit in Fig. 6d leads to the following constraints

$$i_{\rm id} = i_{\rm ed} + \frac{e_{\rm d}}{4Z_{\rm c}} = i_{\rm ed} + i'_{\rm id}$$

(63)

$$i_{\rm ic} = i_+ + i_- = i'_{\rm ic}$$

(64)

where

$$i'_{\rm id} \equiv \frac{1}{2}(i'_{+} - i'_{-})$$

(65)

$$i'_{\rm ic} \equiv i'_+ + i'_- = i_{\rm ic}$$

(66)

and the current through the added DM voltage element is

$$i_{\text{ed}} = i_{+} - i'_{+} = i'_{-} - i_{-}$$

(67)

Finally, applying KVL results in two equations

$$v_{\rm sc} - i_{+}Z_{1} - e_{\rm d} - i'_{-}2Z_{\rm c} - e_{\rm c} = 0$$

(68)

$$v_{\rm sc} - i_{-}Z_2 + e_{\rm d} - i'_{+}2Z_{\rm c} - e_{\rm c} = 0$$

(69)

**Fig. 7** Accuracy improvement for small-mismatch  $A_{vc}$

a Small-mismatch 'zoom-in' of  $A_{vc}$  for  $\Delta Z_f > 0$  (uncorrected). Plotting  $A_{vc}$  for  $\Delta Z > 0$  results in a very similar plot. The calculated line falls on the shorted-input model data instead of the more accurate simulated data

b Small-mismatch 'zoom-in' of  $A_{vc}$  for  $\Delta Z_f > 0$  (corrected). A plot of  $A_{vc}$  for  $\Delta Z > 0$  is very similar. Small-mismatch CM-DM gain agrees well with simulated circuits after the correction is added

Solving these constraints for the 'corrected transconductance',  $Y'_{\rm cd} = (i_{\rm id}/v_{\rm sc})_{v_{\rm cd}=0}$ , leads to

$$Y'_{\rm cd} = \frac{Y_{\rm cc}(\overline{Z_f}\Delta Z + \overline{Z}(\Delta Z_f + a_{\rm c}\overline{Z_f}/1 + a_{\rm d})) - \Delta Z}{4Z_1Z_2 + (1/2)\Delta Z_f\Delta Z}$$

(70)

which is more complicated than the expressions in (59)–(62). Because the small-mismatch region is of interest here,  $Y'_{cd}$  can be simplified with the small-mismatch approximations

$$\Delta Z_f \ll Z_{f1}, Z_{f2}, \overline{Z_f} \tag{71}$$

$$\Delta Z \ll Z_1, Z_2, \overline{Z} \tag{72}$$

which imply that  $Z_{f1}\simeq Z_{f2}\simeq \overline{Z_f}$  and  $Z_1\simeq Z_2\simeq \overline{Z}$ . The 'small-mismatch corrected transconductance' becomes

$$Y'_{\rm cds} \simeq \frac{(a_{\rm c}\overline{Z_f}/1 + a_{\rm d}) - \Delta Z}{2Z_{\rm dm}Z_{\rm cm}}$$

(73)

The denominator in (73) can be forced to match the common denominator from the other three transconductances by multiplying the numerator and denominator by 2 and adding the small quantity,  $\Delta Z_t \Delta Z_t$ , back in

$$Y'_{\rm cds} \simeq 2 \frac{\overline{Z_f(a_{\rm c}/1 + a_{\rm d})} - \Delta Z}{4Z_{\rm dm}Z_{\rm cm} + \Delta Z_f \Delta Z}$$

(74)

Comparing  $Y'_{\rm cds}$  from (74) to  $Y_{\rm cd}$  from (60) reveals that they differ only in the 'correction term' ( $\overline{Z_f}(a_{\rm c}/1+a_{\rm d})$ ). Model validation (Fig. 7b) with this corrected  $Y'_{\rm cds}$  shows

Model validation (Fig. 7b) with this corrected  $Y'_{\rm cds}$  shows good agreement for small mismatch values. Although  $Y'_{\rm cds}$  was calculated while assuming small mismatches, model validations will show that the full model, including the corrected  $Y'_{\rm cds}$ , agrees for the range 0–200% of resistive element mismatch values. Therefore the following results, including  $Y'_{\rm cds}$ , are proposed as the full transconductance—transimpedance descriptive abstraction of the FD voltage

amplifier

$$Y_{\rm dd} = 2 \frac{\overline{Z_f} + \overline{Z}}{4Z_{\rm cm}Z_{\rm dm} + \Delta Z \Delta Z_f}$$

(75)

$$Y'_{\text{cds}} = 2 \frac{\overline{Z_f}(a_c/1 + a_d) - \Delta Z}{4Z_{\text{cm}}Z_{\text{dm}} + \Delta Z \Delta Z_f}$$

(76)

$$Y_{\rm dc} = 2\frac{\Delta Z_f - \Delta Z}{4Z_{\rm cm}Z_{\rm dm} + \Delta Z \Delta Z_f} \tag{77}$$

$$Y_{\rm cc} = 8 \frac{\overline{Z}}{4Z_{\rm cm}Z_{\rm dm} + \Delta Z \Delta Z_{\rm f}}$$

(78)

and the transimpedance amplifier results are repeated here for convenience

$$Z_{\rm dd} = 2\frac{a_{\rm d}\overline{Z_f} - a_{\rm c}\Delta Z_f/2}{(1 + a_{\rm d})} \tag{79}$$

$$Z_{\rm cd} = \frac{1}{2} \frac{a_{\rm c} \overline{Z_f} - a_{\rm d} \Delta Z_f}{(1 + a_{\rm d})}$$

(80)

The results in (75)–(80) yield the full expression for the DM output voltage when substituted into the following expression

$$v_{\rm od} = v_{\rm sd}(Y_{\rm dd}Z_{\rm dd} + Y_{\rm dc}Z_{\rm cd}) + v_{\rm sc}(Y'_{\rm cds}Z_{\rm dd} + Y_{\rm cc}Z_{\rm cd})$$

(81)

# 3.2 Voltage amplifier input impedance

CM and DM input impedances for the voltage-mode amplifier may be taken directly from the transconductances as follows

$$Z_{\text{ind}} \equiv \left(\frac{v_{\text{sd}}}{i_{\text{id}}}\right)_{v_{\text{on}}=0} = Y_{\text{dd}}^{-1}$$

(82)

$$Z_{\rm inc} \equiv \left(\frac{v_{\rm sc}}{i_{\rm ic}}\right)_{v_{\rm sd}=0} = Y_{\rm cc}^{-1}$$

(83)

so that the DM input impedance is

$$Z_{\text{ind}} = \frac{1}{2} \frac{4Z_{\text{cm}}Z_{\text{dm}} + \Delta Z \Delta Z_f}{\overline{Z_f} + \overline{Z}}$$

(84)

and the CM input impedance is

$$Z_{\rm inc} = \frac{1}{8} \frac{4Z_{\rm cm}Z_{\rm dm} + \Delta Z \Delta Z_f}{\overline{Z}}$$

(85)

Simplifying the expressions for DM and CM input impedance with the small-mismatch approximations in (71) and (72) leads to the 'small-mismatch DM input impedance'

$$Z_{\text{ind s}} = Z_{\text{dm}} = Z_1 + Z_2$$

(86)

and the 'small-mismatch CM input impedance'

$$Z_{\text{inc s}} = Z_{\text{cm}} = Z_1 \| Z_2 + \frac{\overline{Z_f}}{2}$$

(87)

which can be approximated for intuition as

$$Z_{\text{inc s}} \simeq Z_1 || Z_2 + Z_{f1} || Z_{f2}$$

(88)

The DM and CM input impedance expressions, especially (86) and (88), are intuitive when following the respective current paths (Fig. 2b) through the amplifier. As one might expect, the special-case impedances,  $Z_{\rm dm}$  and  $Z_{\rm cm}$  from (55) and (56), are related to the input impedances,  $Z_{\rm ind}$  and  $Z_{\rm inc}$  in (84)–(87). In fact,  $Z_{\rm dm}$  and  $Z_{\rm cm}$  are, by definition, special cases of  $Z_{\rm ind}$  and  $Z_{\rm inc}$

$$Z_{\rm dm} = Z_{\rm ind}|_{i_{\rm in}=0} \tag{89}$$

$$Z_{\rm cm} = Z_{\rm inc}|_{i_{\rm id}=0} \tag{90}$$

Moreover, the results in (86) and (87) suggest that those special cases are coincident with small mismatches in the external homologous elements.

### 3.3 Discussion

Familiar quantities such as DM-DM gain,  $A_{\rm vd}$ , and common-mode rejection ratio (CMRR) are readily extracted and simplified from the modularised result. For instance, DM-DM gain in the result from (81) is

$$A_{\rm vd} \equiv \left(\frac{v_{\rm od}}{v_{\rm sd}}\right)_{v_{\rm sc}=0} = Y_{\rm dd} Z_{\rm dd} + Y_{\rm dc} Z_{\rm cd}$$

(91)

and expanding this leads to the full DM voltage gain expression (see (92))

This full-gain expression can be simplified to suit the particular non-idealities of interest. For instance, if mismatches are small, the difference between them is smaller ( $\Delta Z_f - \Delta Z \simeq 0$ ), and the second term in the numerator of (92) can be disregarded leaving only  $A_{\rm vd} \simeq Y_{\rm dd} Z_{\rm dd}$ . In the small-mismatch approximation this

becomes

$$A_{\rm vd} \simeq \frac{4(\overline{Z_f} + \overline{Z})(a_{\rm d}\overline{Z_f} - (1/2)a_{\rm c}\Delta Z_f)}{(4Z_{\rm cm}Z_{\rm dm})(1 + a_{\rm d})}$$

(93)

where the small second-order mismatch term in the denominator has been left out. Expanding the impedances,  $Z_{\rm dm}$  and  $Z_{\rm cm}$ , the DM voltage gain above reduces to

$$A_{\text{vds}} = \frac{(a_{\text{d}}\overline{Z_f} - (1/2)a_{\text{c}}\Delta Z_f)}{\overline{Z}(1 + a_{\text{d}})}$$

(94)

where we define  $A_{\rm vds}$  as the 'small-mismatch DM voltage gain.' In the fully ideal limit,  $a_{\rm d}\to\infty$  and  $a_{\rm c}\to0$

$$A_{\text{vdo}} = \frac{\overline{Z_f}}{\overline{Z}} \tag{95}$$

where we define  $A_{\rm vdo}$  as the 'fully-ideal voltage gain.' The form of  $A_{\rm vdo}$  is consistent with intuition that we bring from SE amplifier cases.

Also from (81), the CM-DM cross-coupling gain is

$$A_{\rm vc} \equiv \left(\frac{v_{\rm od}}{v_{\rm sc}}\right)_{v_{\rm sd}=0} = Y'_{\rm cds} Z_{\rm dd} + Y_{\rm cc} Z_{\rm cd}$$

(96)

and dividing this quantity by the DM-DM gain yields the common-mode rejection

$$CMR \equiv \left(\frac{A_{vc}}{A_{vd}}\right) = \frac{Y'_{cds}Z_{dd} + Y_{cc}Z_{cd}}{Y_{dd}Z_{dd} + Y_{dc}Z_{cd}}$$

(97)

which can be simplified by neglecting small terms to obtain the approximate CMR

$$CMR \simeq \frac{4(\overline{Z_f}(a_c/1 + a_d) - \Delta Z)a_d\overline{Z_f} + 4\overline{Z}(a_c\overline{Z_f} - a_d\Delta Z_f)}{4(\overline{Z_f} + \overline{Z})a_d\overline{Z_f} + (\Delta Z_f - \Delta Z)(a_c\overline{Z_f} - a_d\Delta Z_f)}$$

(98)

The common denominator in the transconductances (75)–(78) divides out, simplifying the calculation above. Collecting terms, approximating  $(1 + a_d) \simeq a_d$ , and rewriting (98) gives

$$CMR \simeq \frac{(a_{c}/a_{d}) - ((\overline{Z}/Z_{f})\Delta Z_{f} + \Delta Z/\overline{Z_{f}} + \overline{Z})}{1 + ((\Delta Z_{f} - \Delta Z)(a_{c}/a_{d} - \Delta Z_{f}/\overline{Z_{f}})/4(\overline{Z} + \overline{Z_{f}}))}$$

(99)

Reducing (99) further with the small-mismatch approximations in (71) and (72), the denominator approaches 1, leaving the numerator and we arrive at the 'small-mismatch common-mode rejection'

$$CMR_{s} = \underbrace{\frac{a_{c}}{a_{d}}}_{\text{op-amp gains'}} - \underbrace{\frac{(\overline{Z}/\overline{Z_{f}})\Delta Z_{f} + \Delta Z}{\overline{Z_{f}} + \overline{Z}}}_{\text{external elements'}}$$

(100)

$$A_{\rm vd} = \frac{4(\overline{Z_f} + \overline{Z})(a_{\rm d}\overline{Z_f} - (a_{\rm c}\Delta Z_f/2)) + (\Delta Z_f - \Delta Z)(a_{\rm c}\overline{Z_f} - a_{\rm d}\Delta Z_f)}{(4Z_{\rm cm}Z_{\rm dm} + \Delta Z\Delta Z_f)(1 + a_{\rm d})}$$

(92)

which is neatly separable into an 'op-amp gain term' and an 'external element term'.

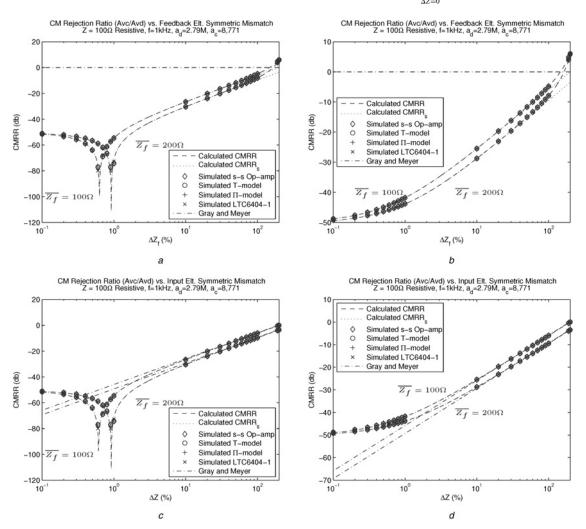

Model validation plots for CMRs in Fig. 8 show good agreement for symmetric mismatches up to about 100% in the feedback and input elements. CMRR is defined here as the logarithmic version of CMR measured in decibels, CMRR  $\equiv 20 \log_{10} |\text{CMR}|$ . For calculating CMR with larger mismatches, the expression in (99) can be used for better accuracy as it is shows good agreement for large percentage mismatch (200%). Numerical results from the half-circuit decomposition analysis in [28] are overlaid on the lower plots. Note that in Figs. 8a and b, the results from [28] are somewhat trivial due to the limitations of the analytical approach employed there.

The model validations also support the well-known fact that the optimal mismatch, yielding the smallest CMR, occurs for non-zero-valued mismatches (see the nulls in Figs. 8a and c). Although significant, the analysis from [28] does not predict this behaviour. The cancellation effect at non-zero-valued mismatch results from the finite DM and CM gains of the op-amp,  $a_{\rm d}$  and  $a_{\rm c}$ , as is clear from the CMR expression in (100). For example, with  $\overline{Z_f}=100\,\Omega$ , the optimal mismatch for the LTC6404-1 for either the feedback or input element mismatch alone is about 0.61% as shown in Fig. 8. In theory, arbitrarily small CMR values could be obtained by adjusting the mismatches to achieve zero-valued CM-DM

gain. In practice, such control over the mismatch is perhaps difficult. The zero-crossing of the CM-DM gain, which leads to the null in the CMRR, is also evident in the plot of Fig. 7b from Section 3.1. Note that the plots for CMRR in Fig. 8 approach the CMRR of the op-amp, -50 dB, for zero-valued mismatches and are also in agreement with (100).

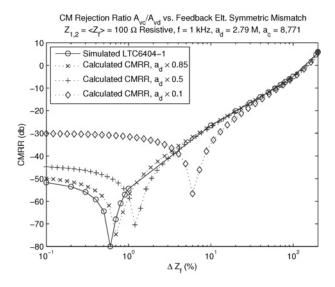

## 3.4 Sensitivity

The results in Sections 2 and 3 have shown good model accuracy having considered op-amp gain parameters,  $a_{\rm d}$  and  $a_{\rm c}$ . Examining the sensitivity of the mathematical model to those parameters may reveal the amount of modelling error caused by uncertainties in our knowledge of the op-amp gain parameters. It may also reveal the amount that particular performance metrics change as op-amp gain parameters vary in time due to temperature effects, and so on. In either case, the simple derivative may be employed to examine the effect of changes in the op-amp gain parameters.

For example, starting from (100), the value of feedback impedance mismatch corresponding to the null in CMRR varies with op-amp gain parameters as follows

$$a_{\rm d} \frac{\partial \Delta Z_f}{\partial a_{\rm d}} \bigg|_{\substack{\rm CMRR \to -\infty}} = -\frac{a_{\rm c}}{a_{\rm d}} \frac{\overline{Z_f}}{\overline{Z}} (\overline{Z_f} + \overline{Z}) \tag{101}$$

Fig. 8 Finite op-amp CM gains,  $a_d$  and  $a_c$ , lead to a null in the CMRR at non-zero mismatch values

- a CMRR for  $\Delta Z_f > 0$

- b CMRR for  $\Delta Z_f < 0$

- c CMRR for  $\Delta Z > 0$

- d CMRR for  $\Delta Z < 0$

$$a_{c} \frac{\partial \Delta Z_{f}}{\partial a_{c}} \Big|_{\substack{\text{CMRR} \to -\infty \\ \Delta Z = 0}} = \frac{a_{c}}{a_{d}} \frac{\overline{Z_{f}}}{\overline{Z}} (\overline{Z_{f}} + \overline{Z})$$

(102)

Analysis regarding the value of input-element mismatch leads to similar results. Note that the error due to changes in  $a_{\rm d}$  is simply the negative of the error due to changes in  $a_{\rm c}$ .

As a numerical example, consider the nominal impedances  $\overline{Z_f} = \overline{Z} = 100 \, \Omega$  and op-amp gain parameters from the simulations above. Using (101), a fractional change in DM opamp gain,  $\partial a_d/a_d = -0.15$ , corresponding to a multiplicative error of 0.85, leads to an error in the location of the null of approximately +0.09% in agreement with the results plotted in Fig. 9. Fig. 9 also illustrates the effect of larger changes in  $a_d$ . Naturally, the zero-mismatch CMRR should increase as  $a_d$  decreases, also in agreement with Fig. 9.

**Fig. 9** Plots of CMRR for various multiplicative errors in op-amp gain  $a_d$  compared to the actual CMRR for the linear technology part LT6404-1

# 3.5 Finite op-amp input impedance

The results above were calculated based on the op-amp model in Fig. 3 and the assumptions described in Section 1.3. Model validation showed excellent agreement among the calculated results and the behaviour of a commercial FD op-amp. In general, there may be a need to include other aspects in the op-amp model. The versatility of the transimpedance amplifier abstraction developed in Section 2 was demonstrated in a first example, by adding to it the input elements,  $Z_1$  and  $Z_2$ , yielding a voltage amplifier. Here, we consider the addition of finite op-amp input impedance to the idealised op-amp model of Fig. 3.

The op-amp input impedance elements can be modelled as shunt impedances at the op-amp input nodes to incremental ground. The addition of those impedances can be viewed as a modification of the voltage amplifier analysis in Section 3 leading to the four transconductances,  $Y_{\rm dd}-Y_{\rm cc}$ . Since the transimpedance amplifier model responses were derived in terms of the input currents  $i_+$  and  $i_-$ , only the voltage amplifier analysis needs to be iterated.

Using the Thevenin equivalent circuits comprising the input voltage sources and impedances  $Z_1$ ,  $Z_2$  and the additional op-amp input impedance elements, (48)–(51) become

$$i_{+}|_{v_{\text{sd}}=0} = \frac{(v_{\text{sc}}(Z_{\text{in 1}}/Z_{\text{in 1}} + Z_{1}) - e_{\text{cc}})}{Z_{1}||Z_{\text{in 1}}|}$$

(103)

$$i_{-}|_{v_{\rm sd}=0} = \frac{(v_{\rm sc}(Z_{\rm in\,2}/Z_{\rm in\,2}+Z_{\rm 2})-e_{\rm cc})}{Z_{\rm 2}||Z_{\rm in\,2}}$$

(104)

$$i_{+}|_{v_{\rm sc}=0} = \frac{((1/2)v_{\rm sd}(Z_{\rm in\,1}/Z_{\rm in\,1} + Z_{1}) - e_{\rm cc})}{Z_{1}||Z_{\rm in\,1}|}$$

(105)

$$i_{-}|_{v_{\rm sc}=0} = \frac{(-(1/2)v_{\rm sd}(Z_{\rm in\,2}/Z_{\rm in\,2}+Z_2)-e_{\rm cc})}{Z_2||Z_{\rm in\,2}}$$

(106)

Starting from these modified constraints, one can re-derive the four tranconductances in terms of op-amp input impedances,

Fig. 10 Simplified schematic of the FD signal conditioning electronics

Fig. 11 Plot of simulated and measured occupancy sensor output data from [25]

$Z_{\text{in 1}}$  and  $Z_{\text{in 2}}$ , while keeping the same results for the two transconductances found in Section 2.

# 4 Experimental validation

This treatment of FD amplifiers was motivated by an investigation of a particular capacitive occupancy sensor. The sensor, presented in [25], employs a FD amplifier connected between two electrodes, to measure changes in a physically balanced bridge network comprising the lumped capacitances between conducting bodies in the detection field. A half-circuit representation of the FD amplifier was not suitable for capturing the effect of the arbitrarily varying capacitive impedances in the bridge network nor was it sufficient to account for the effects of the amplifier's separate DM and CM current paths. Only a generalised model with an unbroken structure could accurately represent these effects. In this application example, the distributed capacitances comprising the bridge network in the capacitive sensor take the place of the impedance elements,  $Z_1$  and  $Z_2$  from Fig. 1. Imbalances in the complicated capacitive bridge network indicate a detection of an occupant. It is precisely those imbalances that must be captured accurately by our model of the FD amplifier. The power of the intermediate FD transimpedance amplifier circuit model from Section 2 is highlighted in this example because it accurately captures the behaviour of the FD structure and its effect on a complicated and intentionally asymmetric impedance network.

Fig. 10 shows a schematic of the signal conditioning electronics for this capacitive sensor including the FD frontend amplifier. The signal processing scheme represented by the electronics in Fig. 10 is synchronous detection, a well-known approach to isolating baseband signals in amplitude modulated carrier signals. Also shown in the figure is a simplified depiction of the lumped element capacitive bridge network. The capacitive impedances in the bridge network correspond to the input impedance elements  $Z_1$  and  $Z_2$  in Fig. 1. The FD front-end amplifier is loaded by a FD multiplier circuit used to synchronously detect modulations of the high-frequency carrier signal caused by the presence of the occupant. More details can be found in [25].

A comparison of experimental and simulated data further validated the analytical modelling in this paper. Experimental data was taken from an implemented capacitive sensor using the electronics shown in Fig. 10. Simulated data was taken from a SPICE simulation of the experimental setup having replaced the front-end amplifier with the circuit model of the FD amplifier in Fig. 4b. Finite op-amp input impedances as well as coaxial shield stray capacitances were included in the simulated model as shunt impedances at the input terminals to the transimpedance amplifier circuit model. In the experimental system from [25], the Texas Instruments FD op-amp part THS4140 was used. Model parameters,  $a_d$  and  $a_c$ , for the FD front-end circuit model were taken from the datasheet for the THS4140 FD op-amp at the signal frequency, 50 kHz in this example. Based on the gain bandwidth product of the THS4140 part, the signal frequency is well below the cross-over frequency for that opamp and so the basic assumptions stated at the beginning of this paper are valid. Significantly, the model validation in this section will serve to prove the utility of the circuit models and analysis developed in this paper for yet another commercial FD op-amp.

Finite-element modelling software, FastCap<sup>®</sup>, was used to determine the values of the lumped element capacitances needed for the SPICE simulation. To simulate a passing occupant, the FastCap<sup>®</sup> simulation was re-run for several different configurations of the system corresponding to different time steps as the occupant passed through the detection field. Details can be found in [25].

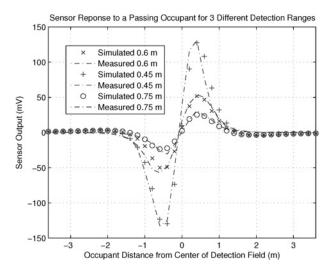

Model validation results showing excellent agreement are plotted in Fig. 11. Data and simulation are shown for three different detection ranges as the occupant passes through the detection field. The detection range is defined as the smallest perpendicular distance between the transmitting (source) electrode in the capacitive sensor and the occupant as the occupant passes through the detection field. Refer to [25] for more details.

# 5 Conclusion

A new approach for small-signal analysis of FD closed-loop op-amp circuits is presented. The approach is built upon the development of a circuit model for a FD transimpedance amplifier. The circuit model of the FD transimpedance amplifier enables analysis and simulation of practical FD circuits and captures the distinct CM and DM paths through the amplifier. Simulated model validation showed excellent agreement between the calculated results and the performance of a commercial FD op-amp. Experimental model validation showed excellent agreement between the behaviour of the simulated FD transimpedance amplifier circuit model and an implemented capacitive sensor employing a FD front-end amplifier.

# 6 Acknowledgment

This work was supported by the US Department of Energy and the Grainger Foundation.

# 7 References

Arsalan, M., Shamim, A., Roy, L., Shams, M.: 'A fully differential monolithic LNA with on-chip antenna for a short range wireless receiver', *IEEE Microw. Wirel. Compon. Lett.*, 2009, 19, (10), pp. 674–676

- 2 Sewiolo, B., Fischer, G., Weigel, R.: 'A 30 GHz variable gain amplifier with high output voltage swing for ultra-wideband radar', *IEEE Microw. Wirel. Compon. Lett.*, 2009, 19, (9), pp. 590–592

- 3 Chattier, S., Schleicher, B., Feger, T., Purtova, T., Schumacher, H.: '79 GHz fully integrated fully differential SI/SIGE HBT amplifier for automotive radar applications'. 13th IEEE Int. Conf on Electronics, Circuits and Systems, ICECS'06, December 2006, pp. 1011–1014

- 4 Cornett, K., Fu, G., Escorcia, I., Mantooth, H.: 'SIGE BICMOS fully differential amplifier for extreme temperature range applications'. IEEE Aerospace Conf., March 2009, pp. 1–10

- 5 He, X.-Y., Pun, K.-P., Kinget, P.: 'A 0.5-V wideband amplifier for a 1-MHz CT complex delta-sigma modulator', *IEEE Trans. Circuits Syst. I: Reg. Pap.*, 2009, **56**, (11), pp. 805–809

- 6 Spinelli, E.M., Garcia, P.A., Guaraglia, D.O.: 'A dual-mode conditioning circuit for differential analog-to-digital converters', *IEEE Trans. Instrum. Meas.*, 2010, 59, (1), pp. 195–199

- 7 Weiss, J., Majoux, B., Bouvier, G.: 'A very high gain bandwidth product fully differential amplifier'. Proc. Ninth Int. Conf. on VLSI Design, January 1996, pp. 99–102

- 8 Pletersek, A., Strle, D., Trontelj, J.: 'Low supply voltage, low noise fully differential programmable gain amplifiers'. Proc. European Design and Test Conf., ED TC 1995, March 1995, pp. 105–112

- 9 Karki, J.: 'Fully-differential amplifiers'. Texas instruments application report, August 2000

- 10 Karki, J.: 'Analysis of fully-differential amplifiers'. Texas instruments application report, 2005

- 11 A.D. Inc.: 'Differential drivers for high speed ADCS overview', Analog Devices Tutorial MT-075, 2009

- 12 Nordeng, A.: 'Fully differential amplifier with rail-to-rail outputs offers 16-bit performance at 1 MHz on a single 2.5 V supply'. Linear Technology Magazine, December 2005

- 13 Coporation, L.T.: 'Lt6404 datasheet' (Milipitas, CA)

- 14 Haspeslagh, J., Sansen, W.: 'Design techniques for fully differential amplifiers'. Proc. IEEE Custom Integrated Circuits Conf., May 1988, pp. 12.2/1–12.2/4

- 15 Lee, T.-S., Chung, H.-Y., Cai, S.-M.: 'Design techniques for low-voltage fully differential CMOS switched-capacitor amplifiers'. Proc. IEEE Int. Symp. on Circuits and Systems, ISCAS, 2006, p. 4

- 16 Sin, S.-W.S.-P.U., Martins, R.: 'Generalized circuit techniques for low-voltage high-speed reset- and switched-opamps', *IEEE Trans. Circuits Syst. I, Reg. Pap.*, 2008, 55, (8), pp. 2188–2201

- 17 Dessouky, M., Kaiser, A.: 'Very low-voltage fully differential amplifier for switched-capacitor applications'. Proc. 2000 IEEE Int. Symp. on Circuits and Systems, ISCAS 2000, Geneva, 2000, vol. 5, pp. 441–444

- 18 Peeters, E., Steyaert, M., Sansen, W.: 'HF measurement procedure for fully differential building blocks'. Instrumentation and Measurement Technology Conf., 1996

- Xu, G., Embabi, S.: 'A systematic approach in constructing fully differential amplifiers', *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, 2000, 47, pp. 1343–1347

Hurst, O.J., Lewis, S.H.: 'Determination of stability using return

- 20 Hurst, O.J., Lewis, S.H.: 'Determination of stability using return ratios in balanced fully differential feedback circuits', *IEEE Trans. Circuits Syst. II: Analog Digit. Signal Process.*, 1995, 42, (12), pp. 805–817

- 21 Crovetti, P., Fiori, F.: 'Finite common-mode rejection in fully differential operational amplifiers', *Electron. Lett.*, 2006, 42, (11), pp. 615–617

- Wu, R., Makinwa, K., Huijsing, J.: 'The design of a chopped current-feedback instrumentation amplifier'. IEEE Int. Symp. on Circuits and Systems, ISCAS, May 2008, pp. 2466–2469

Xie, H., Fedder, G.: 'A CMOS z-axis capacitive accelerometer with

- 23 Xie, H., Fedder, G.: 'A CMOS z-axis capacitive accelerometer with comb-finger sensing'. 13th Annual Int. Conf. on Micro Electro Mechanical Systems, January 2000, pp. 496–501

- 24 Zhang, G., Xie, H., de Rosset, L., Fedder, G.: 'A lateral capacitive CMOS accelerometer with structural curl compensation'. 12th IEEE Int. Conf. on Micro Electro Mechanical Systems, January 1999, pp. 606–611

- 25 Cooley, J.J., Avestruz, A.-T., Leeb, S.B.: 'A retrofit capacitive sensing occupancy detector using fluorescent lamps', *IEEE Trans. Ind. Electron.*, *Special Issue on Modern Ballast Technology*, March 2011, accepted for publication

- 26 Middlebrook, R.D.: 'Differential amplifiers' (Wiley, 1963)

- 27 Giacoletto, L.J.: 'Differential amplifiers' (Wiley, 1970)

- 28 Gray, P.R., Hurst, P.J., Lewis, S.H., Meyer, R.G.: 'Analysis and design of analog integrated circuits' (Wiley, 2001)

- 29 Middlebrook, R.D.: 'Low-entropy expressions: the key to designoriented analysis'. 21st Annual Conf. on IEEE Frontiers in Education, September 1991, pp. 399–403

- 30 Cooley, J.J.: 'Analysis, modelling and design of energy management and multisource power systems'. PhD dissertation, Massachusetts Institute of Technology, Cambridge, MA, USA, 2011